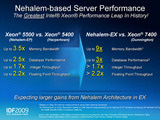

1TBのメモリが利用可能-メインフレーム並みの信頼性を持つ「Nehalem-EX」

9月に米国のサンフランシスコで開催された米Intelの開発者セミナー「IDF(Intel Developer Forum) 2009」では、MP(Multi Processor)サーバー向けCPU「Nehalem-EX(コード名:Beckton)」を使ったサーバーが登場した。年内から2010年の初めに出荷される予定だ。今回は、このNehalem-EXを取り上げる。

■Nehalem-EXのハードウェア構成

|

| 8コアを持つNehalem-EXは、4ソケットで32コア(64スレッド同時実行)のメインフレーム級のサーバーCPUだ |

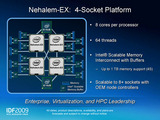

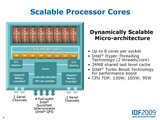

Nehalem-EXは、1CPUあたり8コアを持ち、Hyper Threadingにより同時に16スレッド処理できるヘビー級のCPUだ。4ソケットサーバーでNehalem-EXを使用すれば、物理CPUコアが32コア、Hyper Threadingを利用することで同時に64スレッドが処理できる。

Nehalem-EXの個々のCPUコアは、現在リリースされているNehalemで使用されているCPUコアと同じだ。CPUの1次キャッシュは64KB(命令キャッシュ32KB+データキャッシュ32KB)、2次キャッシュは256KBを持っている。

ただし、3次キャッシュメモリは、Xeon 5500番台(Nehalem-EP)とは少し異なる。Xeon 5500番台は、4コアで8MBの3次キャッシュメモリを共有していた。しかし、Nehalem-EXでは、CPUコアごとに3MBの3次キャッシュメモリを持ち、それぞれの3次キャッシュメモリは、リング状のバスに接続され、トータル24MBの3次キャッシュメモリを構築している。

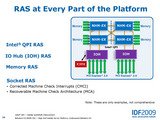

命令セットや仮想化機能なども、Xeon 5500番台とほとんど同じだ。ただし、Nehalem-EXでは、RAS(Reliability、Availability、Serviceability:信頼性、可用性、保守性)機能が用意されているので、RAS関連の命令が追加されている。

【お詫びと訂正】初出時、次世代Itaniumとソケット互換がある旨、記載しておりましたが、事実と異なりました。お詫びして訂正します。

■QPIはCPUあたり4本に

|

| Nehalem-EXは、6コアのXeon 7400番台(Dunnington)よりも、メモリバンド幅で9倍、データベースパフォーマンスで3倍ものパフォーマンスを持つ |

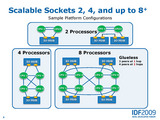

Nehalem-EXは、1CPUあたり4本のQPI(QuickPath Interconnect)を持っている。QPIは、1本あたり6.4GT/秒のデータ転送速度となっている。

Nehalem-EXは、高速のQPIをCPUとI/Oハブとの接続に利用する。例えば、4ソケットのサーバーなら、1つのCPUから3本のQPIを使い、ほかのソケットに接続する。残りの1本は、I/Oハブとの接続に使われる。

Nehalem-EXは、4ソケットサーバーが最適なデザインといえるが、8ソケットサーバーも構築することができる。ただし、トポロジー的に、CPUが1本のQPIで、ほかのCPUと接続されているというデザインにはならない。また、あまり遅延が起こらないように最大でも2ステップで、目的のCPUにアクセスできるようになっている。

この8ソケットサーバーのデザインは、各CPUが持つメインメモリに別のCPUがアクセスするときにペナルティがかさむ(遅延が大きい)ため、あまり一般的には使われないだろう。

|  |

| Nehalem-EXのブロック図。2つのIMCがそれぞれ2チャンネルのメモリを持つ | Nehalem-EXは、4ソケットを標準に、8ソケット、2ソケットといったサーバーで利用できる |

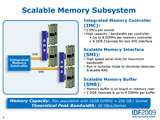

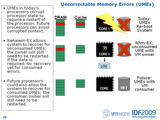

■1TBのメモリが利用可能に

Nehalem-EXは、最大16本のDDR3メモリをサポートしている。16GB DIMMを使用した場合、1CPUあたり最大256GBのメモリをサポートする。もし、4ソケットのサーバーに最大容量を搭載すれば、1TBのメモリが搭載されたメインフレーム級のIntel 64サーバーとなる。

これだけのメモリをサポートするため、Nehalem-EXはXeon 5500番台と比べてメモリコントローラ関連が大幅に変更されている。

Xeon 5500番台では、CPUが直接、DDR3メモリを3チャンネルサポートしていた。一方、Nehalem-EXは、シリアル接続のScalable Memory Interface(SMI)をサポートしたIntegrated Memory Control(IMC)ユニットが2つ内蔵されている。

1つのIMCあたり、2本のSMIをサポートしている(CPUあたり4本のSMI)。SMIは、シリアルインターフェイスのため、そのままではDDR3メモリを接続できない。そこで、シリアル/パラレル変換の機能とメモリバッファーの機能を持った、Scalable Memory Buffer(SMB)に接続される。DDR3メモリは、SMB経由でCPUと接続する。

SMBは、2つのDDR3メモリチャンネルをサポートしており、1チャンネルあたり2本のDIMMが使用できる。

■36レーンのPCI Express 2.0をサポートするチップセット

|

| I/Oハブは、36レーンのPCI Express 2.0インターフェイスをサポートしている。これを自由に組み合わせて、バンド幅を設定することができる |

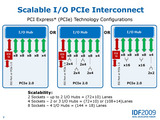

Nehalem-EXは、Xeon 5500用のIntel 5520 I/Oハブをベースとしたものが使用される。ただし、RAS機能をサポートするために、開発コード名「Boxboro-EX」というI/Oハブチップが使用される。

Boxboro-EXがサポートするインターフェイスとしては、PCI Express 2.0が36レーン、2GB/sのスピードを持ったDMI(Direct Media Interconnect)インターフェイスを経由して、USBやSATAなどのインターフェイスをサポートしたI/Oコントローラハブ(ICH)10がサポートされている。このPCI Express 2.0は、フレキシブルな組み合わせにできる。例えば、PCI Express 2.0×8を4本をPCI Express 2.0×16を2本にまとめることも可能だ。

標準的な4ソケットのサーバーでは、I/Oハブを2つ使用する(I/Oハブを3つにすることもできる)。2つのI/Oハブにより、PCI Express 2.0×8が8本、PCI Express 2.0×4が2本の高い拡張性を持ったサーバーを構成できる。

■RAS機能によりシステムを動かし続ける

|

| Nehalem-EXの最大機能機能がRAS機能だ。RAS機能は、CPUだけでなく、QPI、メモリ、I/Oハブにまで及ぶ |

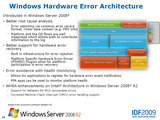

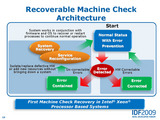

Nehalem-EXの最大の特徴といえるのが、RAS(Reliability、Availability、Serviceability:信頼性、可用性、保守性)機能だ。RAS機能は、さまざまなモジュールにトラブルが起こったとしても、そのモジュールを切り離すことで、システム全体をダウンさせずに動かし続ける機能だ。

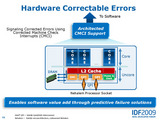

Nehalem-EXは、Corrected Machine Check Interrupts(CMCI)とRecoverable Machine Check Architecture(MCA)という機能を持っている。

例えば、Nehalem-EXのあるCPUコアにトラブルが起こった場合は、OSと協調して、トラブルをチェックして、CPUを再設定(8個あるCPUコアを7個で動かす)して、システムダウンを起こさずにシステムを動かし続ける。もちろん、ハードウェアだけでなく、OSがトラブルをチェックして、OS側でも再設定する必要がある。

このため、Nehalem-EXのRAS機能は、OS側でサポートされている必要がある。IDFでは、VMwareのESX、MicrosoftのWindows Server 2008 R2などのOSで、Nehalem-EXのRAS機能のデモが行われた。このほか、NovellのSUSE Linux、Red HatのRed Hat Enterprise LinuxなどのOSでも、Nehalem-EXのRAS機能をサポートする予定だ。

|  |

| CPUのエラーは、CMCIによりOSに伝えられる | OSは、CMCIからの割り込みにより、トラブルを関知して、リカバリーを行う |

Nehalem-EXのRAS機能は、CPUコアだけでなく、CPUのアンコア部分(I/Oなど)、QPI、メモリ、I/Oハブなど、多岐にわたる。例えば、QPIにトラブルが起きた場合、QPIに接続されているものがCPUなのかI/Oハブなのかをチェックする。その後、トラブルが起きたQPIに接続されているものが、CPUならば自動的にそのCPUを切り離して、システムを再設定する。

メモリの場合は、Nehalem-EXのSMI(Scalable Memory Interface)ごとに、切り離しを行うことができる。このため、1枚のDIMMにトラブルが起こっても、SMB(Scalable Memory Buffer)ごと切り離される。

I/OハブのRAS機能としては、I/Oハブ自体のトラブルに対応する。さらに、I/OハブのPCI Express 2.0に接続されているインターフェイスカードにトラブルが起きたとしても、カード自体を切り離すことができる。もちろん、PCI Express 2.0では、ホットプラグをサポートしているため、トラブルのあったカードをシステムダウンさせずに、入れ替えることも可能だ。

■ハイパーバイザーもRASをサポート

|

| 今年年末ごろにリリースされるVMware ESX 4.1では、ハイパーバイザーでRAS機能がサポートされている。CPUコアにトラブルが起こっても、ESXがリカバリーを行う |

RAS機能によりハードウェアのトラブルがチェックできても、上位レイヤーのOSやハイパーバイザーがハードウェアのトラブルを知って再設定できなければ、システム全体として動作し続けることができない。

VMwareのESXなどのハイパーバイザーやWindows Server 2008 R2などのOSがRAS機能をサポートする場合、ハイパーバイザーがどのCPUでどういった動作が行われているかをきちんと把握している必要がある。例えば、あるCPUコアのキャッシュメモリにトラブルが起こった場合、トラブルが起こったときにどのような動作が行われていたのかログが保存されていないと、ほかのCPUコアが動作を肩代わりすることができない。単に、トラブル部分を切り離すだけでは、OSにとってはシステムダウンを起こす原因となるのだ。

もちろん、ログは、CPUコアだけでなく、メモリやQPI、I/Oハブなど、さまざまな部分に関連する。ハイパーバイザーやOSは、このログをチェックして、トラブルのあったブロックをダイナミックにシステムから切り離し、その後、残りのハードウェアでトラブルのあったブロックを肩代わりして、動作するように設定する。これにより、大規模なシステムでもシステムダウンを起こさずに、ITシステムを動かし続けることができる。

■2010年後半には32nmプロセスの改良版が登場

|

| IntelのサーバーCPUのロードマップ |

Nehalem-EXは、2010年後半には、次世代のWestmereコア(Nehalemの32nmプロセス改良版)へと移行する。WestmereコアのMPは、CPUコアは12コアになる予定だ。Hyper Threading利用時には、同時に24スレッドが実行できる(開発コード名は、Eagleton)。

Nehalem-EXの登場により、各社が独自テクノロジーで実現していたRASは、スタンダード化が行われるかもしれない。

スタンダード化されれば、リーズナブルな価格で高い信頼性、高可用性を持つIntel 64サーバーが、さまざまなサーバーベンダーから発売されることになるだろう。リーズナブルな価格で高い信頼性を持つIntel 64サーバーが発売されれば、多くの企業がメインフレームからIntel 64アーキテクチャーへのリプレースを行う可能性もある。Nehalem-EXは、仮想化だけでなく、基幹システムという面でも注目が集まるだろう。

2009/10/19/ 00:00